导语 在电子工程的深夜里,无数工程师为信号完整性(SI)和电源完整性(PI)问题抓狂。示波器上的波形震荡、眼图闭合,往往让我们陷入迷茫。

其实,很多问题的根源在于我们对“信号”的认知还停留在小学阶段。今天,让我们剥开“0”和“1”的表象,深入物理本质。在高速数字电路的世界里,你画的从来都不是一根“电线”,而是一条“波导”。

我们经常挂在嘴边的一句话是:“信号从发送端跑到了接收端”。这句话在低速世界勉强成立,但在高速世界里,它是一个巨大的误区。

误区一:是电子在跑吗? 如果真是电子一路狂奔,那信号的速度将受限于电子的漂移速度(通常非常慢,约几毫米每秒)。但现实是,信号可以在纳秒级跨越整个PCB板。真正跑的不是电子,而是电磁扰动。

误区二:是电压在跳变吗? 电压高低只是接收端“看到”的结果,而不是传播的过程。当你按下开关的瞬间,驱动器在信号导体和参考导体之间建立了一个时变电场,这个电场又激发出时变磁场。

核心观点:

高速数字信号,本质上是受传输结构约束传播的电磁波。

数字信号的“数字”二字,描述的是信息的编码方式(0和1),而它的物理载体,本质上仍然服从麦克斯韦方程组的电磁场规律。你看到的高电平和低电平,只是这束波在特定时刻、特定位置被“截获”的快照。

[电磁场在PCB微带线中的分布示意图]

你可能会问,为什么在51单片机或者低速逻辑电路里,我们不需要考虑这些复杂的物理场?

1. 集总参数 vs. 分布参数 在低速电路中,信号的波长(或上升时间)远大于PCB走线的物理长度。此时,信号在连线上的传播延迟可以忽略不计。我们用一个简单的电阻、电容模型就能近似它,这叫“集总参数模型”。

2. 边沿速率是关键 所谓的“高速”,很多时候不是由时钟频率定义的,而是由信号的上升/下降时间定义的。

· 低速: 边沿缓慢,高频成分少,场效应不明显。

· 高速: 边沿越快(如现代芯片的纳秒甚至皮秒级边沿),信号包含的高频成分就越多。

3. 量变引起质变 一旦信号的有效高频成分对应的波长,与互联(PCB走线)的尺寸进入同一个量级,传播延迟、反射、损耗就会迅速显性化。这时候,你面对的不再是一个静态的连线问题,而是一个真实的电磁波传播问题。

当你进入高速领域,你会发现工程师的语言突然变了。低速世界讨论的是电压、电流、电阻;而高速世界讨论的是:

· 传输线: 信号走的路。

· 特征阻抗: 电磁波在通道里的“摩擦力”。

· S参数: 信号在通道里的得失。

为什么会有这些概念?因为我们要解决的是波动问题。

直觉: 提供电流回路。 物理本质: 场的回路要连续。 如果参考平面不连续,电磁场的分布就会发生畸变,导致阻抗突变,进而产生反射和辐射。

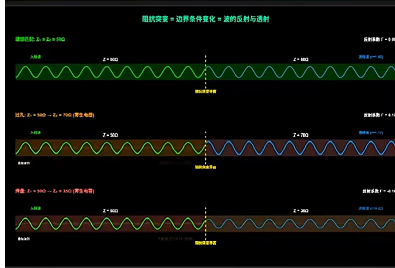

直觉: 信号反弹了。 物理本质: 波遇到边界条件变化就会反射。 就像光从空气射入水中会发生折射和反射一样,电磁波遇到阻抗不连续点(如过孔、连接器、线宽变化),一部分能量会反射回源端,造成振铃。

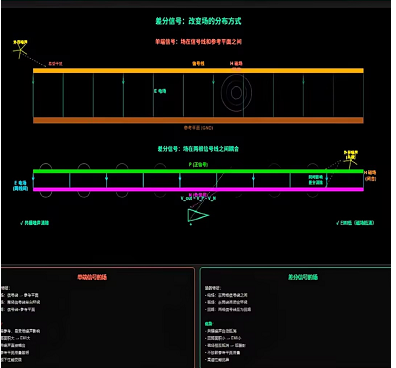

直觉: 两根线抵消了噪声。 物理本质: 改变了场的分布方式。 差分信号通过两根线紧密耦合,使得电磁场主要集中在两根信号线之间,对外界的辐射极小,同时对外界的干扰也具有极强的共模抑制能力。

⚡ 为什么低速不用管?因为“场”还没来得及显灵

1. 参考平面为什么必须连续?

2. 为什么阻抗突变会带来问题?

3. 为什么差分信号更抗干扰?

[单端信号与差分信号电磁场分布对比图]

明白了上述原理,我们对PCB设计的认知必须进行一次升维。

你画的不是“线”,是“通道”。

PCB上的每一个几何细节,都在改写电磁波的传播环境:

· 信号线与参考平面: 决定了电场的建立。

· 介质材料: 决定了波的传播速度和损耗。

· 线宽与线距: 决定了特征阻抗的大小。

· 过孔与焊盘: 这些往往是瓶颈,因为它们在改写局部的边界条件。

设计的核心任务: 给受结构约束传播的电磁波,设计一条连续、可控、低失真的通道。

最后,让我们把这件事压缩成一句话:

高速数字信号的“数字”描述的是编码,而它的物理传播本质上仍然是电磁场问题。

当你下次面对一块高速PCB时,请尝试切换视角。不要问“信号到了没有”,而要问:

· 这束波在通道里经历了什么?

· 它有没有被反射?

· 有没有被介质吸收损耗?

· 有没有因为结构不连续而失真?

如果你能用这种“波动”的视角去审视每一个过孔、每一段走线,那么困扰你的信号完整性问题(SI)、电源完整性问题(PI)以及电磁兼容问题(EMC),都将变得不再神秘。下一次,我们将深入探讨这套语言的核心——差分信号的S参数。